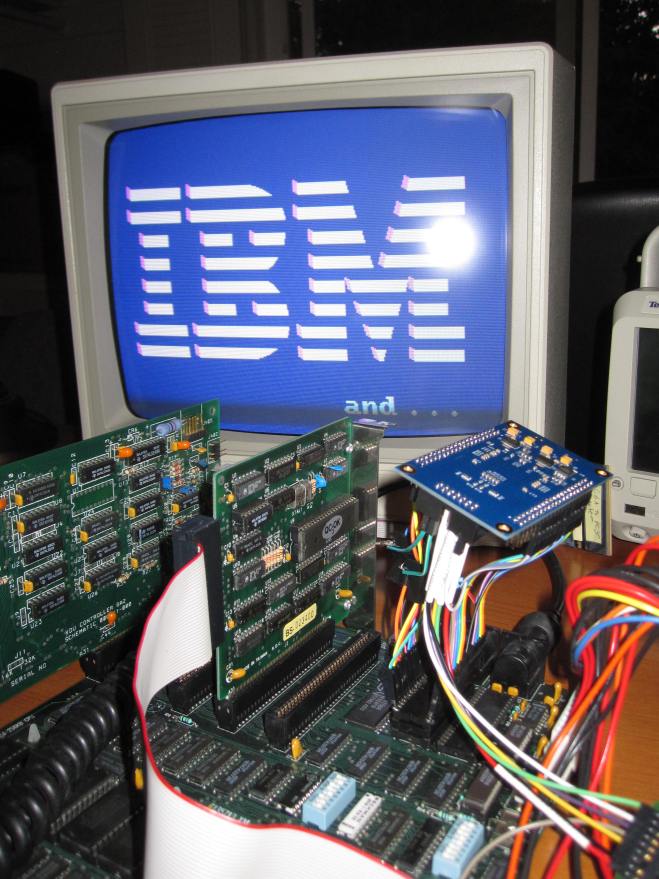

I just finished porting the MCL86 microsequencer-based 8088 core with a minimum-mode BIU (Bus Interface Unit) to a Xilinx Kintex-7 FPGA for use in an IBM PCjr! Here are some videos of the PCjr in action:

IBM PCjr Music running on the MCL86 microsequencer based 8088 FPGA core

IBM PCjr Minuet running on the MCL86 microsequencer based 8088 FPGA core

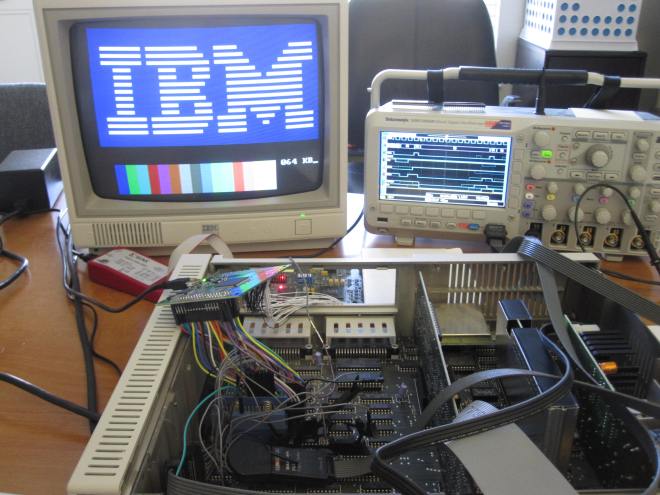

The Xilinx Kintex-7 IOs are not 5V tolerant, so I added a Lattice ispMACH 4256ZE to translate between the Kintex and the PCjr’s motherboard.

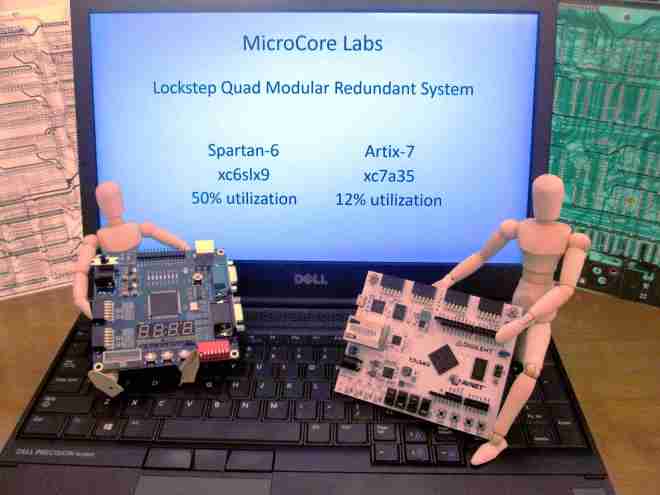

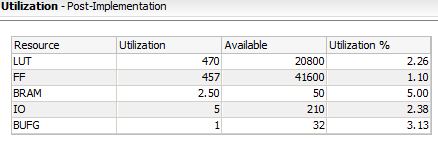

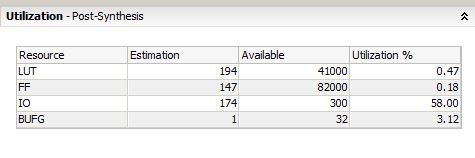

The MCL86 core combined with the minimum-mode 8088 BIU consumes 1.5% of the Kintex-70T FPGA! Four block RAMS are used to hold the microcode.

It is interesting to note that when I disabled the cycle-accuracy of the MCL86 core, the PCjr would no longer pass it’s POST test. It would always beep twice and then enter a HALT state. It appears that there is a test that depends on a particular completion time. Perhaps a timer test?

What I did to bypass this was to disable cycle-accuracy until the first NMI was received which should happen either at the end of the POST when the user makes the first key-press, or when the PCjr receives the keyboard “I am OK” information during it’s POST.

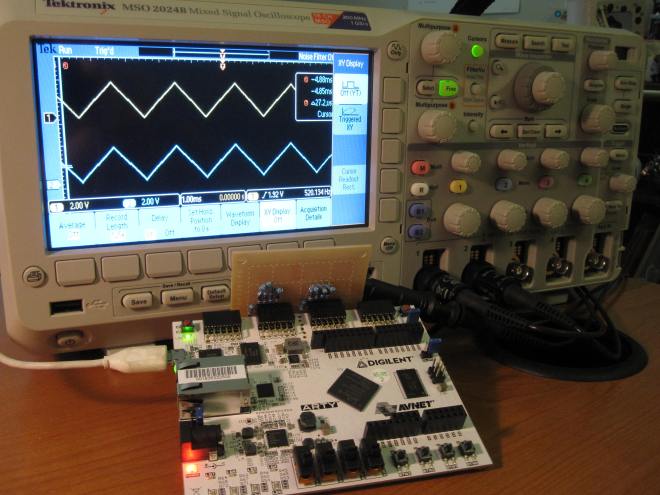

The PCjr runs noticeably faster when the cycle accuracy is disabled. The disk drive seek is faster and the warning bell when you try to use the keyboard when the CPU is busy is a higher pitch.

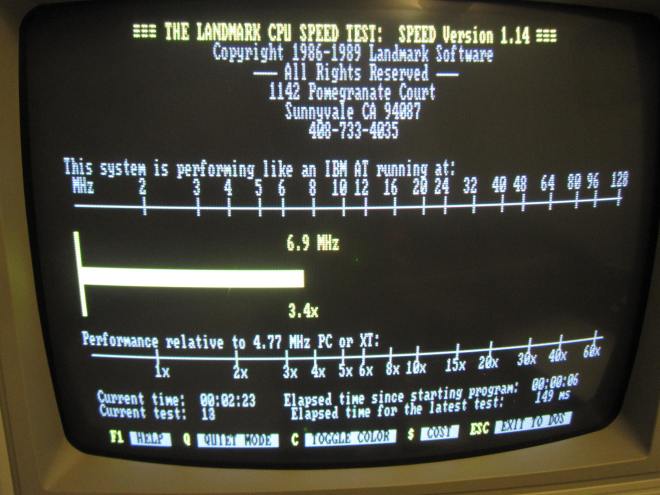

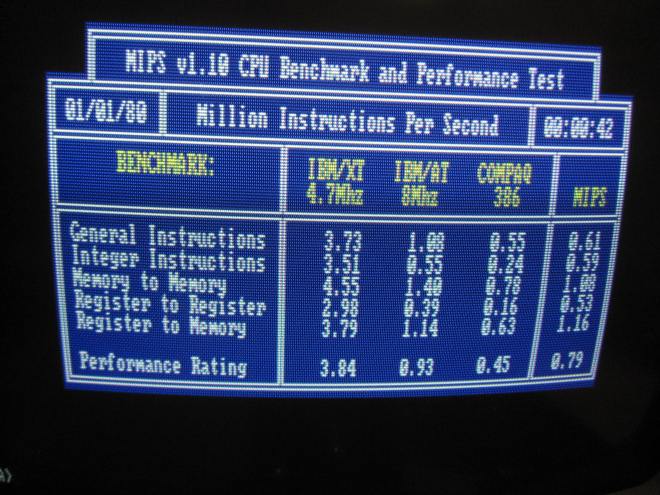

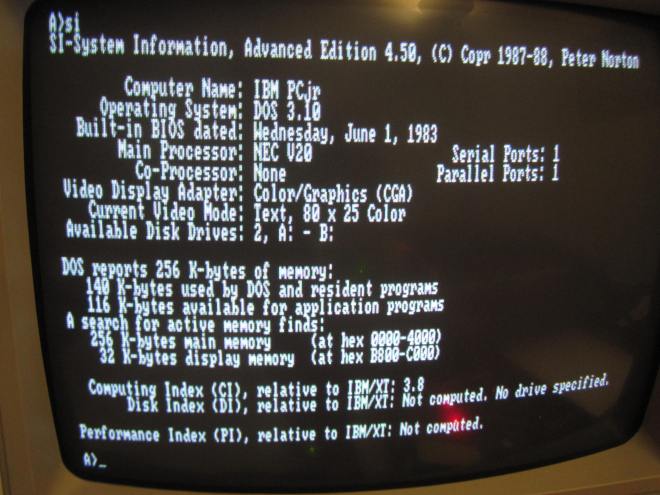

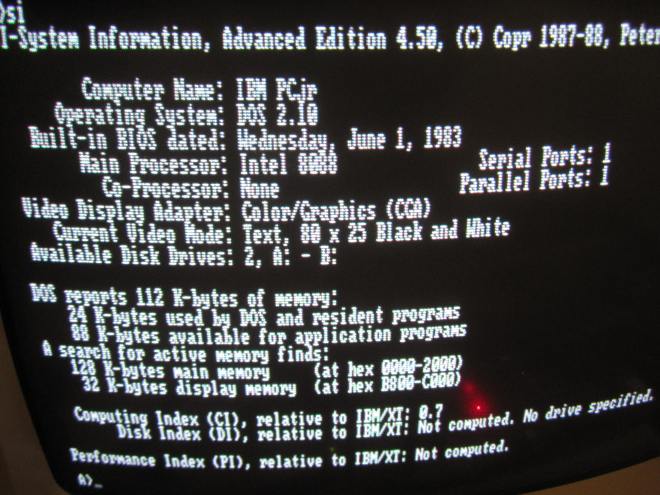

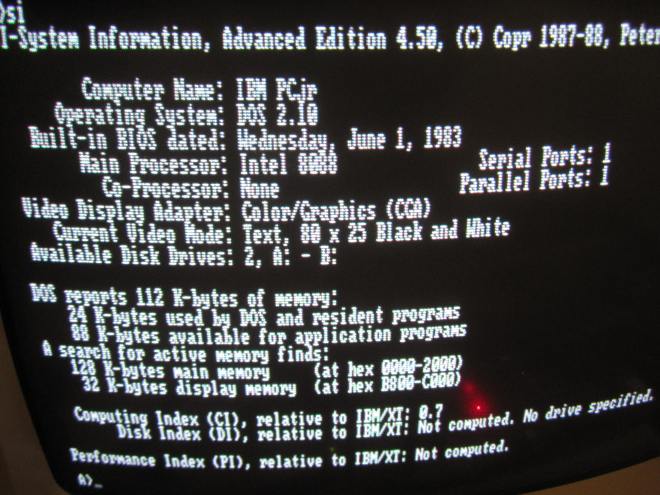

Here is the Norton Utility SI.EXE program running when cycle accuracy is enabled.

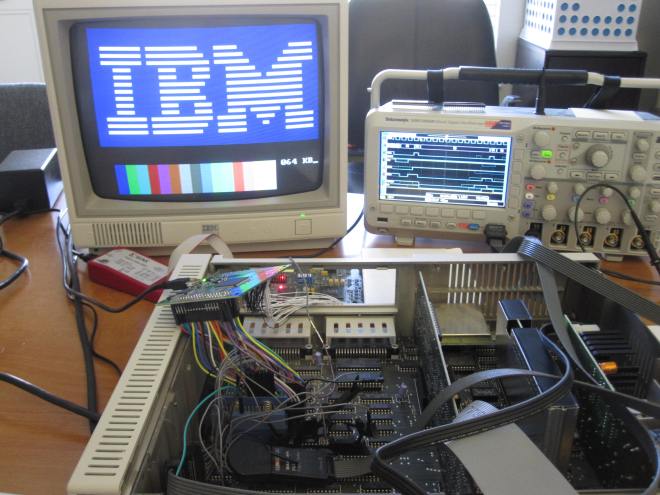

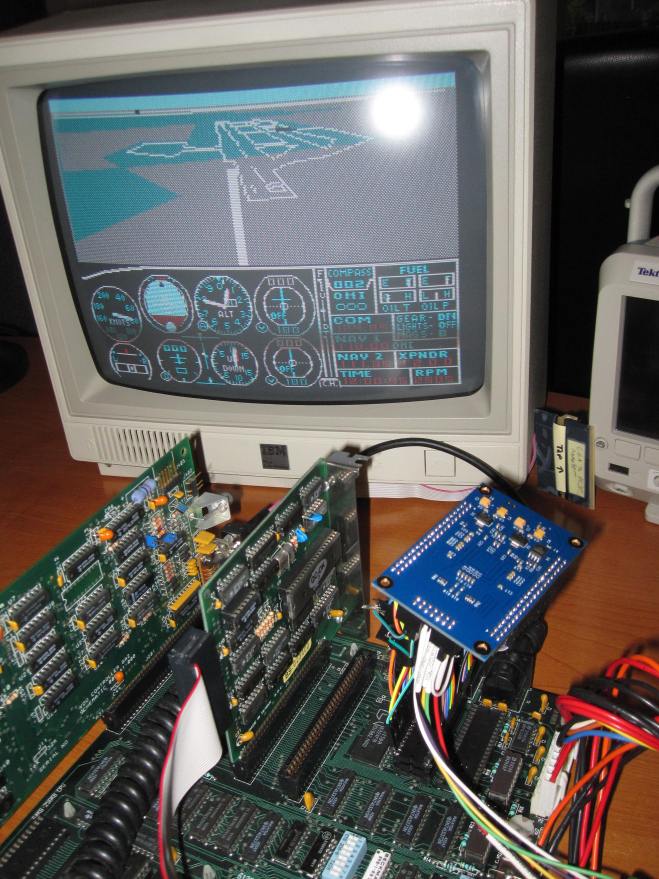

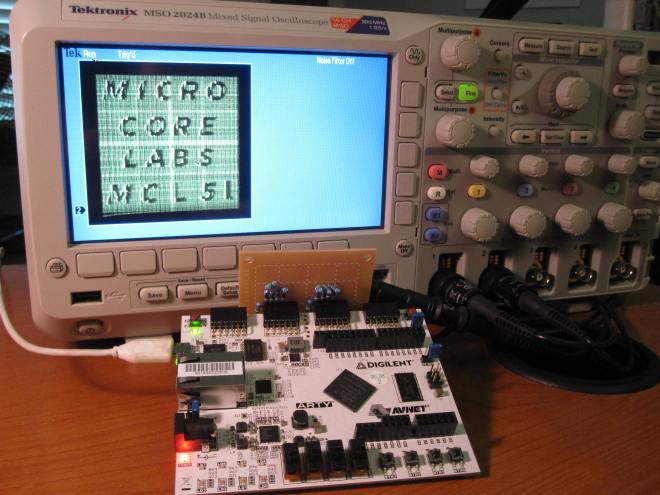

Below is a close-up of the FPGA setup. From the left there is a DIP-clip attached to the 8259 Interrupt Controller so I can probe the 8088 databus. Next to this is the 8088 adapter that is wired to the Lattice ispMACH 4256ZE breakout board which translates between the 5V motherboard and the 3.3V Xilinx Kintex FPGA. The Lattice board is wired to a board that contains the Kintex-7 FPGA.

My next project will be to integrate some of the PCjr’s memory into the FPGA which will be accessed at the processor’s core speed to see how much performance I can squeeze out of a PCjr! The MCL86 core is a 16-bit processor and runs at 100Mhz, so theoretically should be able to access an on-FPGA RAM more than 10X faster than memory on the motherboard!

Please visit us at: www.MicroCoreLabs.com for more information.