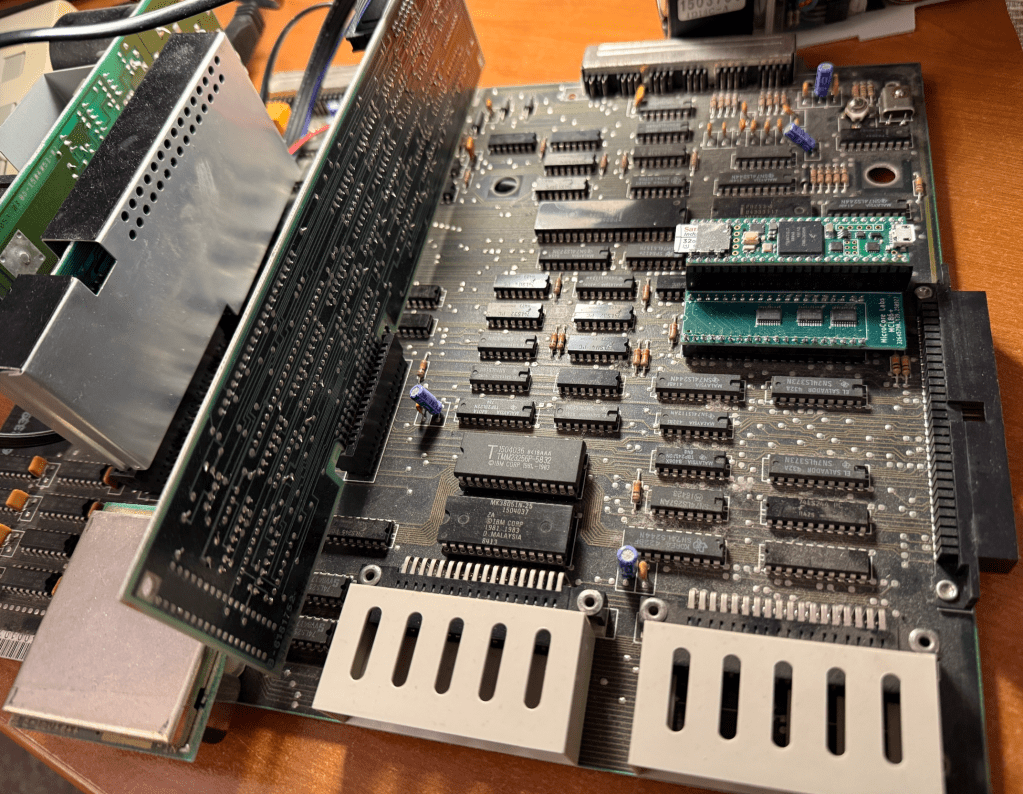

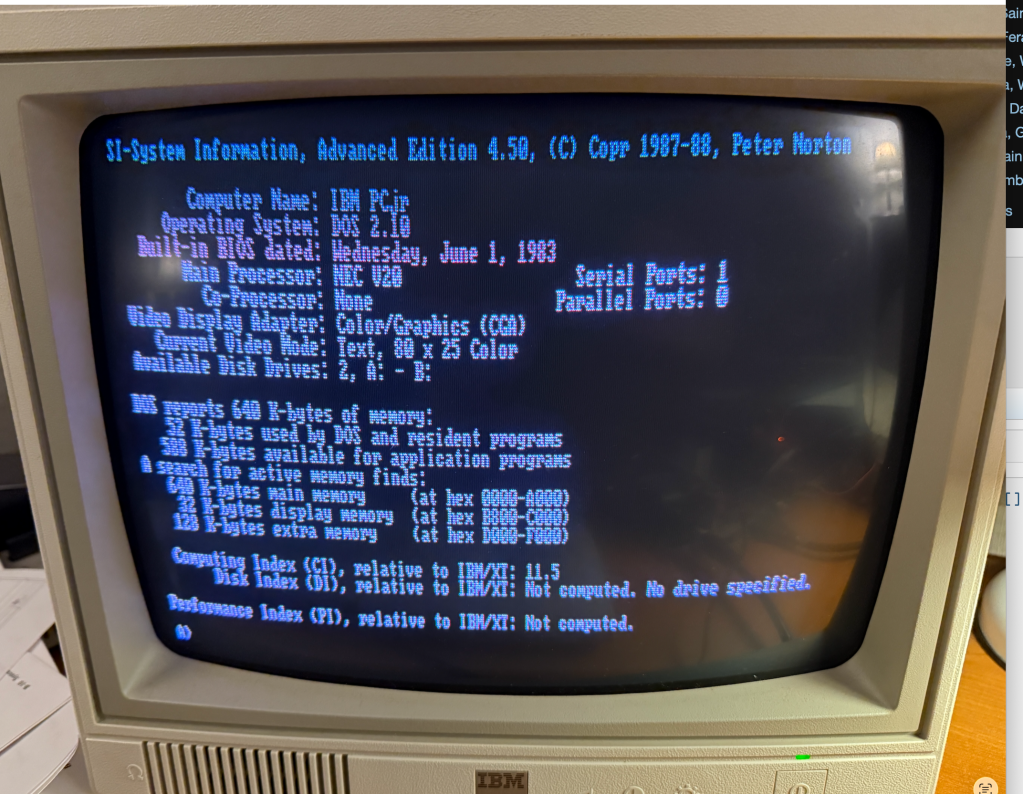

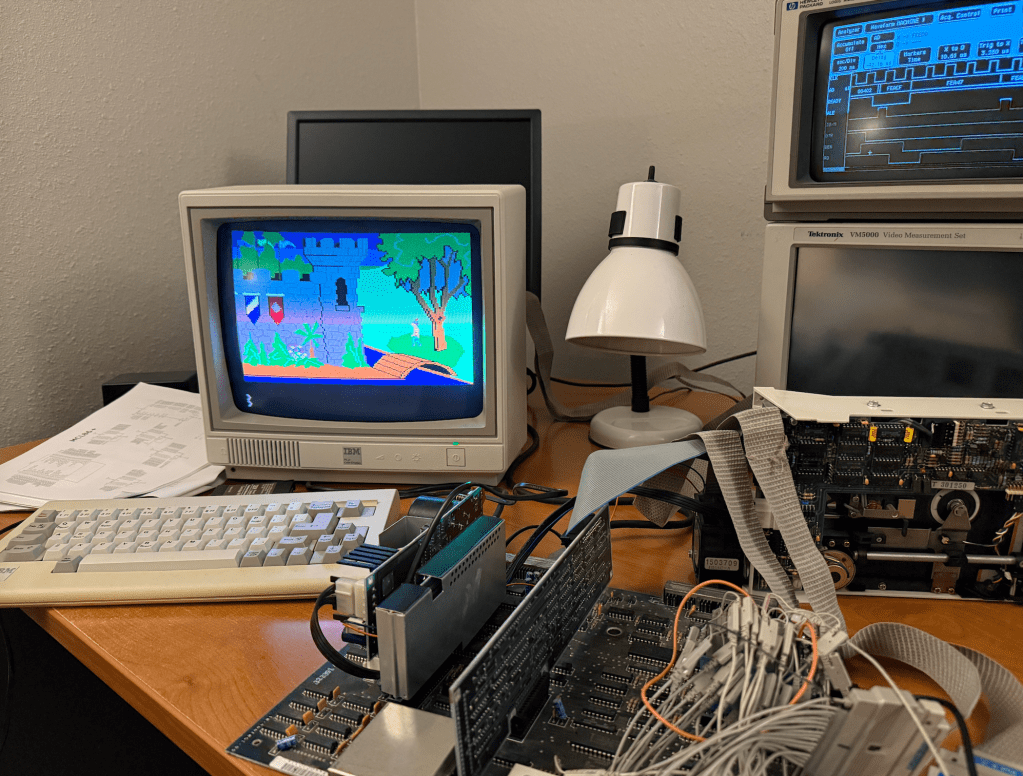

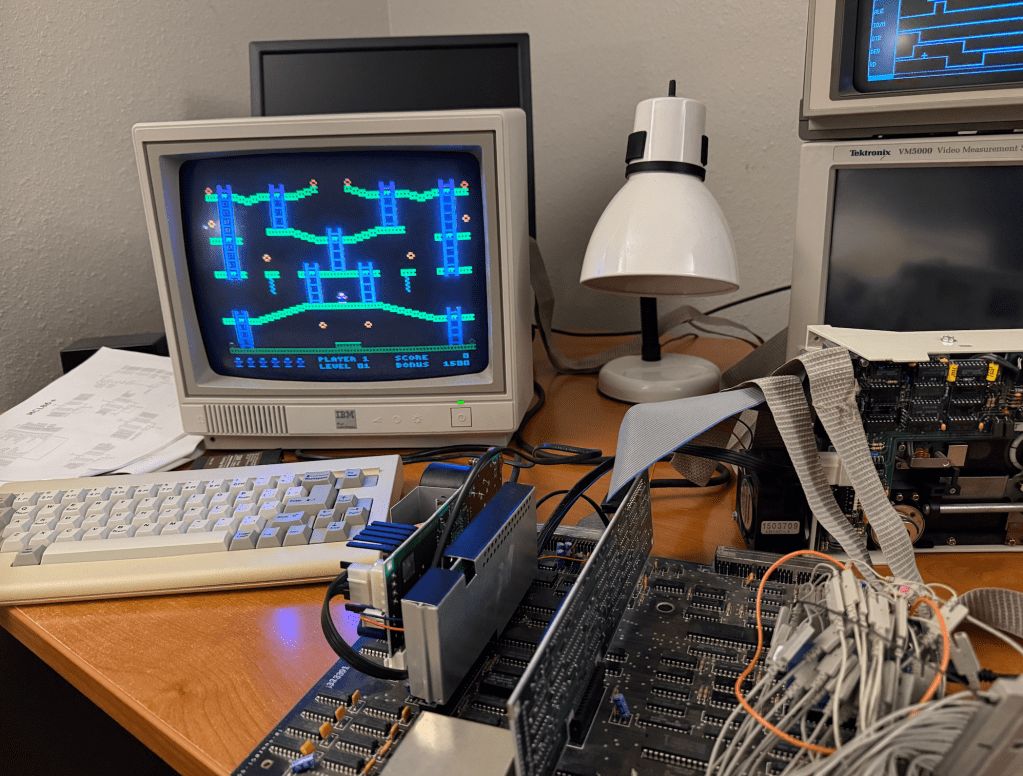

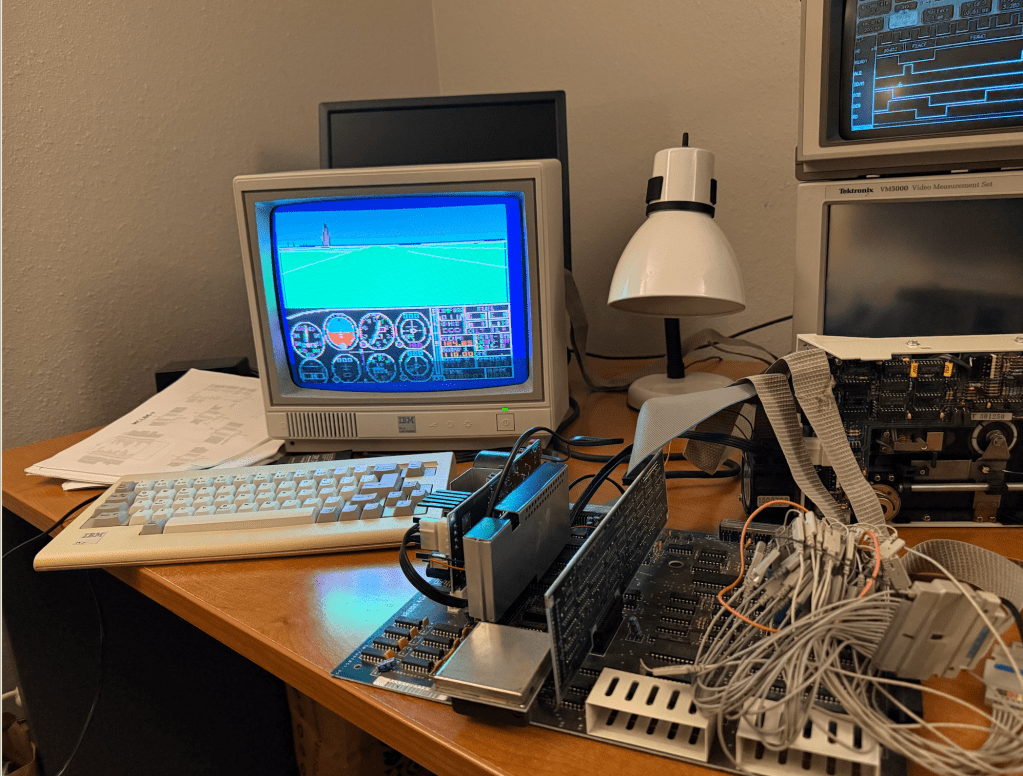

I got the MCL86+ running on the IBM PCjr by adding 8088 minimum mode support plus a few modifications to the PCB.

Project on GitHub: https://github.com/MicroCoreLabs/Projects/tree/master/MCL86%2B

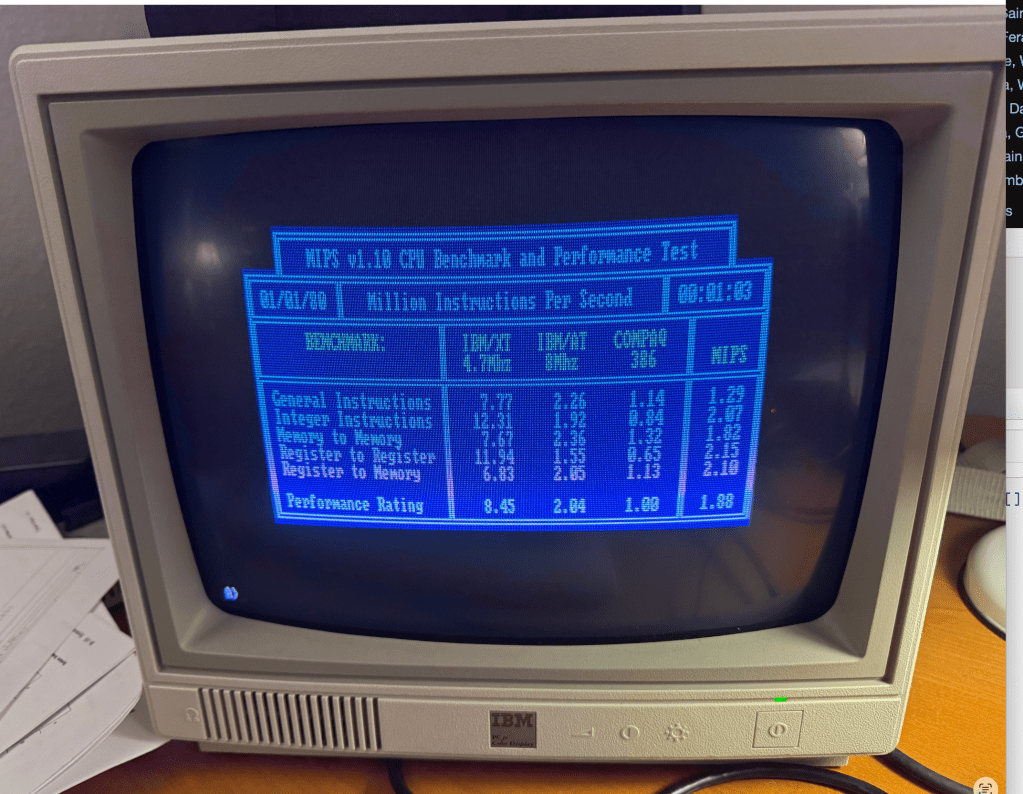

Cycle accurate mode appears to work fine so I next added some acceleration by removing clock counting and mirroring all 640 KB inside of the Teensy. According to MIPS.COM, this IBM PCjr is as fast as a 80386.

The only issue I am running into is the inability to write to the floppy drive. Reads work fine but writes are inconsistent. I’m fairly sure I know why…

Early in the development of the MCL86jr+ I found that the PCjr BIOS is very (overly) reliant on 8088 instruction and bus timing.

Here is what I found:

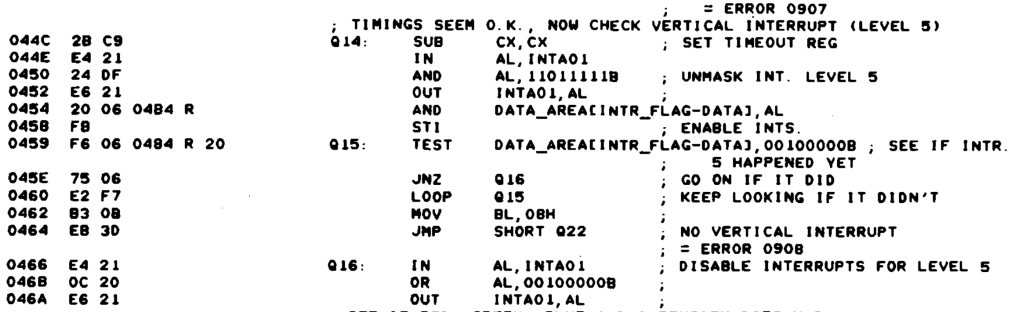

In the BIOS POST CRT Attachment Test the MCL86jr+ would fail with ERROR 0908 and halting. Once I compared the sequence on a logic analyzer with a genuine 8088 I could see that the MCL86+ was performing opcode prefetches at the end of opcodes while the real 8088 interspersed them throughout the opcode execution. This resulted in the MCL86jr+ opcode execution being “tighter” and ready to accept interrupts earlier than the genuine 8088 could.

Shortly after the OUT opcode at address 0xF0452 which enables the vertical retrace interrupt was executed, the MCL86jr+ would accept and process the interrupt which disabled the source even before the main loop at address 0xF0459 had started. This code is not well written and is dependent on specific bus timing and recognition of the interrupt.

Also, I am certain that interrupts were already enabled before address 0x0F458, so the STI opcode should not have been necessary. I wonder if they added it as an attempt to guarantee that interrupts would not be accepted until at least the end of the TEST opcode. (They knew that interrupts are not accepted at the end on the STI opcode). Seems like a sloppy solution.

My guess is that there is another timing-dependent piece of code somewhere in the floppy write routine which is not tolerant of big differences in the MCL86jr+’s approach to opcode and bus timing.

You can reach me at: mailto:eastwood90@hush.com