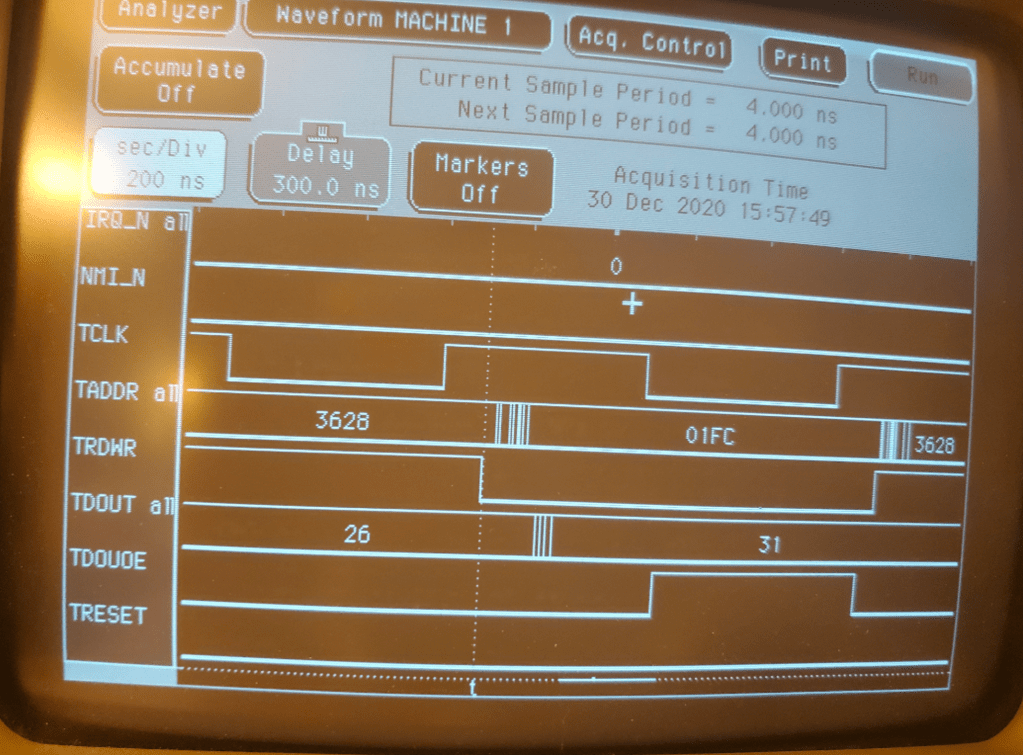

I used a logic analyzer to observe the 6502 bus timing that I able to achieve and it appears to have under 300ns clock to out for the address bus which is within spec. It is difficult to implement parallel GPIO input and outputs with the Teensy 4.1, so I decided to use parallel inputs for the received data[7:0] and sequential writes for each bit of the address bus. I will try to perform parallel writes to GPIO6 directly, but I believe there could be issues with unwanted bits being updated…